This is the most common concept studied in VLSI, and hence most important. We tend to understand the definition but the concept creates confusion at times. Let us revisit this topic in simple terms.

Setup Time

The time before the active clock edge, when the data signal is not allowed to change its value

Hold Time

The time after the active clock edge, when the data signal is not allowed to change its value.

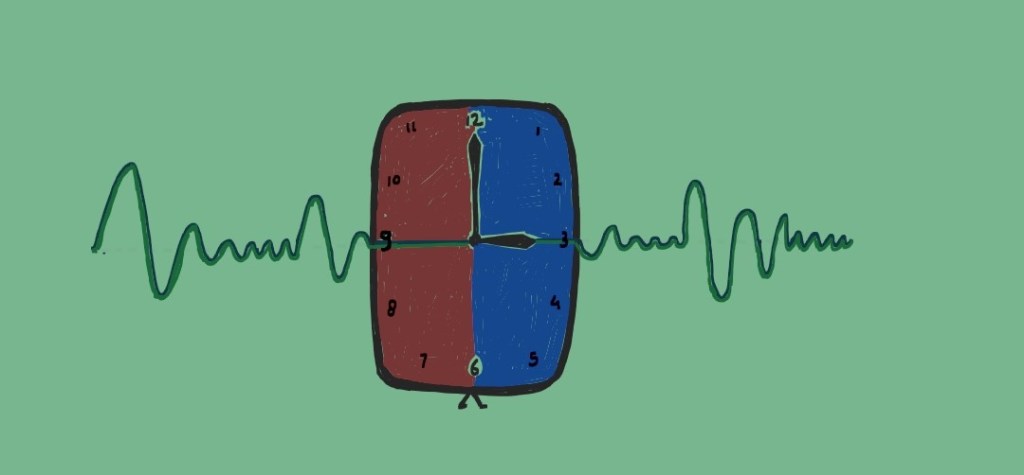

Lets take an example of two flops as given in Figure 3. There are two flops FF1 and FF2 where FF1 acts as the launch flop and FF2 acts as capture flop.

Assumption: Clock reaches both the flops at the same time.

Setup Time

We make sure that the data launched by FF1 doesn’t change anywhere in the red region for being captured correctly by FF2. Else, it will cause metastability as FF2 will not know which value (0 or 1) to capture.

Equations:

Time taken by the data signal to reach FF2 from FF1 (Arrival Time) = Tc-q + Tcomb

The time where signal is not allowed to change is ‘Tsetup’.

The data launched at clk edge ‘A’ will reach clk edge ‘B’ after one time period i.e. ‘Tperiod’

Hence, maximum time for data to reach FF2 (Required time) => Tperiod – Tsetup

To avoid data being changed during setup time interval of clk edge B, Arrival Time < Required Time

Tc-q + Tcomb < Tperiod – Tsetup

Hold Time

We expect that the data launched by FF1 should reach FF2 at the next clock. If it reaches the FF2 on same clock edge, data gets corrupted. It is a hold time violation as the data changes in the blue region.

Equations:

Time taken by the data signal to reach FF2 from FF1 (Arrival Time) = Tc-q + Tcomb

The time where signal is not allowed to change is ‘Thold’.

Here, we do not consider ‘Tperiod’, because the Hold check is done on the same clock edge.

Hence, minimum time for data to reach FF2 (Required Time) => Thold

To avoid data being changed in the same clk edge A, Arrival Time > Required Time

Tc-q + Tcomb > Thold

Skew Addition

Assumption: Clock reaches FF2 ‘Tskew’ units later than FF1.

Arrival Time: Tc-q + Tcomb

Required Time: Tperiod – Tsetup + Tskew

Tc-q + Tcomb < Tperiod – Tsetup + Tskew

Increasing skew eases timing restriction for setup, as it increases the difference between required and arrival times (based on above equation), providing enough margin for the design.

Arrival Time: Tc-q + Tcomb

Required Time: Thold + Tskew

Tc-q + Tcomb > Thold + Tskew

Reducing skew eases the timing here, as it increases the difference between required and arrival time to provide enough margin for the design.

Leave a comment