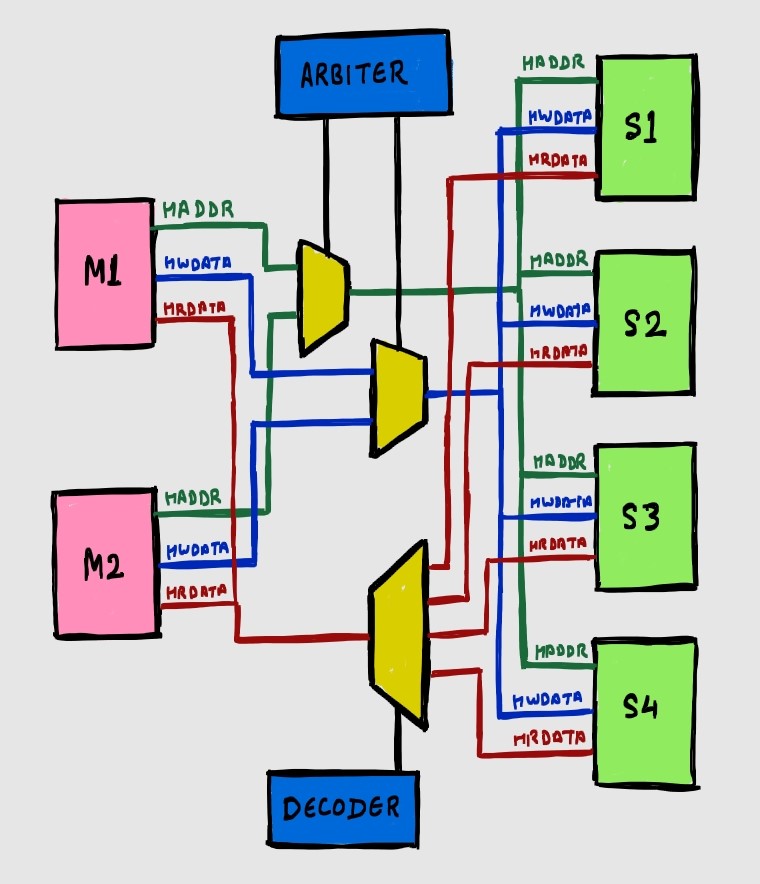

There are many functional blocks in an SoC, which need to communicate with each other. AMBA (Advanced Microcontroller Bus Architecture) is one such specification by ARM, which defines on-chip communication standards. AHB and APB are two distinct buses under AMBA. An example of an AMBA system is given in Figure 1.

We will focus on AHB in this article.

- AHB Masters: DMA, DSP

- AHB Slaves: Internal/external memories

AMBA AHB can have following components. The components are shown in Figure 2, along with master and slave connections.

AHB Master:

- Can initiate read/write operations

- Only one master can be active at a time

AHB Slave:

- Responds to read/write operations

- Gives acknowledgement to the master

AHB Arbiter:

- If multiple masters request the bus access at the same time, it decides which master wins.

AHB Decoder:

- Decodes the address of each transfer to select the slave.

Operation:

- One or more master asserts a request signal to the arbiter.

- Arbiter grants access to one master.

- Master drives address and control signals (address, direction of transfer – read/write, width of transfer, type of transfer)

- The Address decoder asserts HSEL signal for the chosen slave, where transfer is intended.

- The data is transferred. Write bus moves data from master to slave, while read bus moves data from slave to master

- Address states cannot be extended but data states can be extended by holding ‘HREADY’ signal LOW. (HREADY = 0 inserts wait states)

- Slave provides the response to the master using HRESP[1:0]. The different values of HRESP indicate following cases:

OKAY

Transfer completed successfully

ERROR

Transfer is unsuccessful

RETRY/SPLIT

Transfer cannot complete but master can continue attempting the transfer

Transfer Protocol:

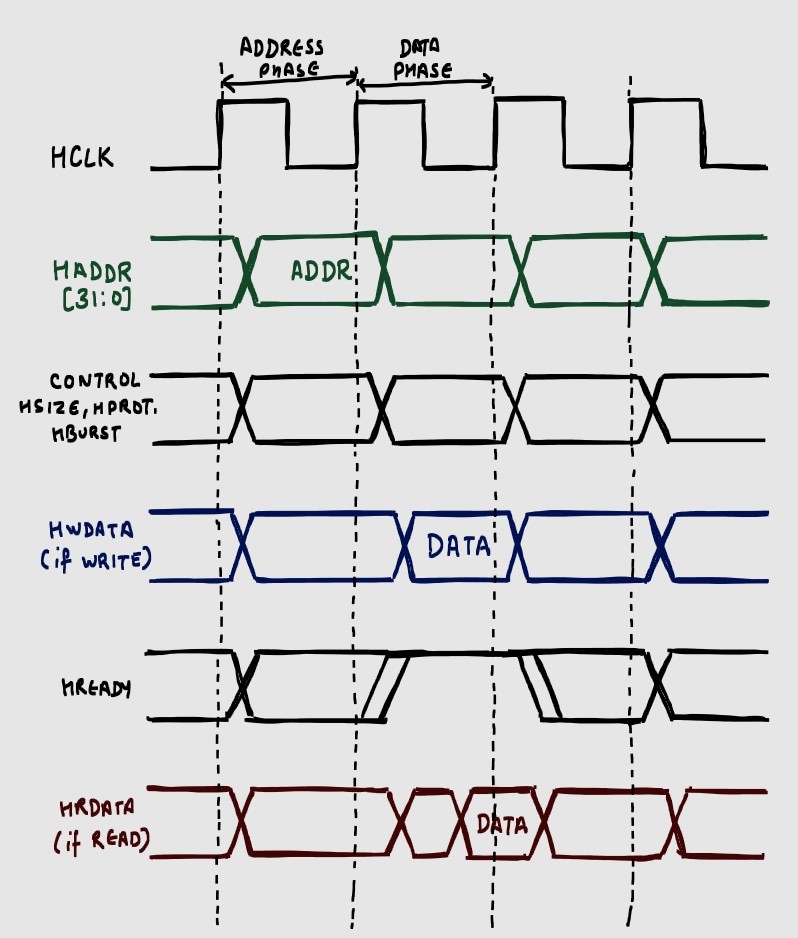

The transfer protocol is shown in Figure 3. There are two phases: Address (one cycle), Data (one or more cycles)

- Master drives the signals after first clock edge

- Slave samples the data at second clock edge

- Slave starts the appropriate response at third rising edge

How HREADY Helps?

HREADY can be pulled ‘LOW’ during data phase to allow additional time for completion (specially, if data is getting transferred over different frequencies).

- READ: Slave can wait for these extended cycles unless it has required data available.

- WRITE: The data written by master remains on the data bus throughout the extended cycles.

HREADY has a major role to play in BURST transfers, which we will study in further articles.

Leave a reply to Vishal Mishra Cancel reply