Parameter :

While coding a Verilog module, there can be a constant value that needs to be used multiple times within the module. Such constants can be declared using ‘parameter’.

Advantage : The biggest advantage of using ‘parameters’ is that, the code is scalable. A change in parameter value can be easily accommodated by the design.

Example: Assume you are writing a code to count numbers until ’20’. So, you defined a parameter as:

parameter COUNT_LIMIT=20

Now, if you want the counter to go until ’30’, only the parameter value needs to be re-assigned and the code will remain the same.

Usage of ‘parameter’ :

Let us suppose we need 4 counters each counting up-to a different value. This means that the counter variable needs to have different width to accommodate different counting limit. The module can be defined as follows:

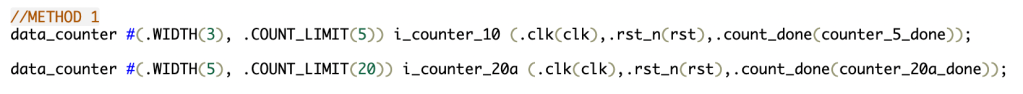

The ‘parameter’ constants ‘WIDTH’ and ‘COUNT_LIMIT’ can be changed during module instantiation as follows:

This method does not need to follow the order of parameters defined in the module.

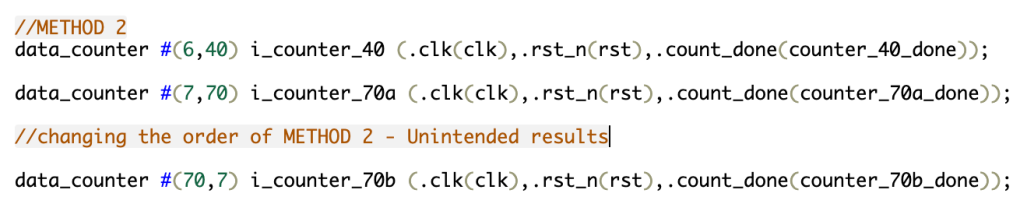

This method needs to follow the order of how parameters are defined in module definition. If the order is reversed as shown in Figure 3, the counter will only counter WIDTH will become ’70’, and COUNT_LIMIT will become ‘7’ (which is not the intention).

Important points to remember:

- Parameter definitions can only be made within a module.

- Can be changed by ‘defparam‘ but not encouraged.

defparam data_counter.WIDTH=6 ;

This is discouraged as ‘defparam’ allows you to change the parameter from any other module. This may lead to conflict and will be difficult to debug where the parameter’s value was changed.

`DEFINE

- Alongside parameters, there are Macro Definitions, which can be made globally (inside or outside the module). The simple syntax of using macro is:

`define CYCLE_COUNT 40

Points to remember:

- `define can be used anywhere within a file while parameter can only be declared inside a module.

- The use of `define will be compilation order dependent. This means that if 10 files are in the list of compilation, and `define CYCLE_COUNT 40 appears in 5th file, only the next files will be able to use this macro.

- `define macro can be redefined at another place as well. This will give a warning which might be missed and hence, can lead to unintended results.

- `define macros can pass values to parameters as follows:

Guideline 1: To avoid the issue of `define being changed at many places, the guideline is to place all the `define macros in one file, and read it as first file during compilation.

Guideline 2: Use parameter to define constants within the local scope of a module, and use `define only for constants which have a global usage requirement.

LOCALPARAM

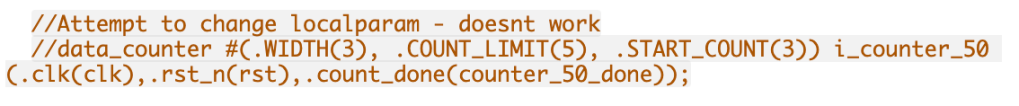

This is a type of constant which can only be declared locally within a module. This cannot be changed when the module is instantiated.

The module ‘data_counter’ used above has START_COUNT defined as localparam, because all the counters need to be started from ‘1’. This value cannot be changed while instantiating the module.

All the examples are given in the module and testbench code here at EDAplayground. Feel free to play around the code, experiment and ask further questions.

Source : New Verilog-2001 Techniques for Creating Parameterized Models (or Down With `define and Death of a defparam!) Clifford E. Cummings Sunburst Design, Inc. cliffc@sunburst-design.com

Leave a comment