You will come across RESETs even in simplest designs, making it one of the most important topic to discuss. Lets dive in…..

A Reset is a signal which forces the design into a known state. This unique and important capability can be used to:

- Initialize any hardware (usually at the beginning of simulation)

- Power-up a device

- Recover a design from an error/unknown state (occurring due to some problem)

Types of Reset:

Synchronous

Reset affects the flip-flop only at an active clock edge. It is applied just like any other input signal in the design.

– Design cannot reset without a clock

+ Timing is easier

+ Reset signal is less prone to glitches, as it is synchronous to the clock (changes only on active clock edge). Clock filters the glitches between clock edges.

– The reset needs to be asserted long enough for the clock to capture the assertion at active clock edge.

– Cannot work in designs where clock is gated, as there is no clock to capture the reset signal once clock is gated off.

Asynchronous

Reset affects the flip-flop at any time, whenever the signal is asserted/de-asserted. It is a high priority signal.

+ Design can reset even without a clock

+ Data path is independent of the reset signal, hence the design is high-speed

– Reset glitches can be a problem

– If the reset signal changes close to the clock edge, the flip-flop can go into metastability.

– There can be two kinds of designs:

Clock gated: Asynchronous resets are safe to use because the clock starts after the reset is deasserted.

No clock gating: In this case, if asynchronous reset is de-asserted close to the active edge of the clock, it can cause problems.

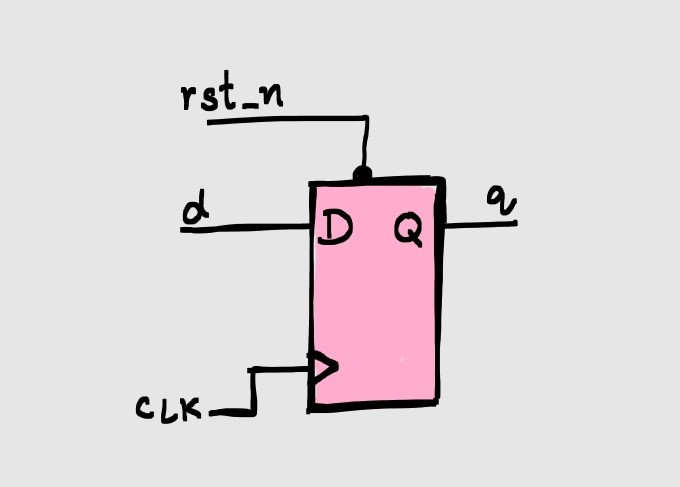

Verilog Modelling

always @(posedge clk)

if (!rst_n)

Q <= 1’b0;

else

Q <= D;

end

always @(posedge clk, negedge rst_n)

if (!rst_n)

Q <= 1’b0;

else

Q <= D;

end

Leave a comment