The major part of DFT is converting a design into a scannable design where all the flip flops are connected in a network of scan chains. With more complex designs, and many scan chains to handle, hierarchical DFT comes into play. This methodology involves wrapper chain structure, which will be discussed here.

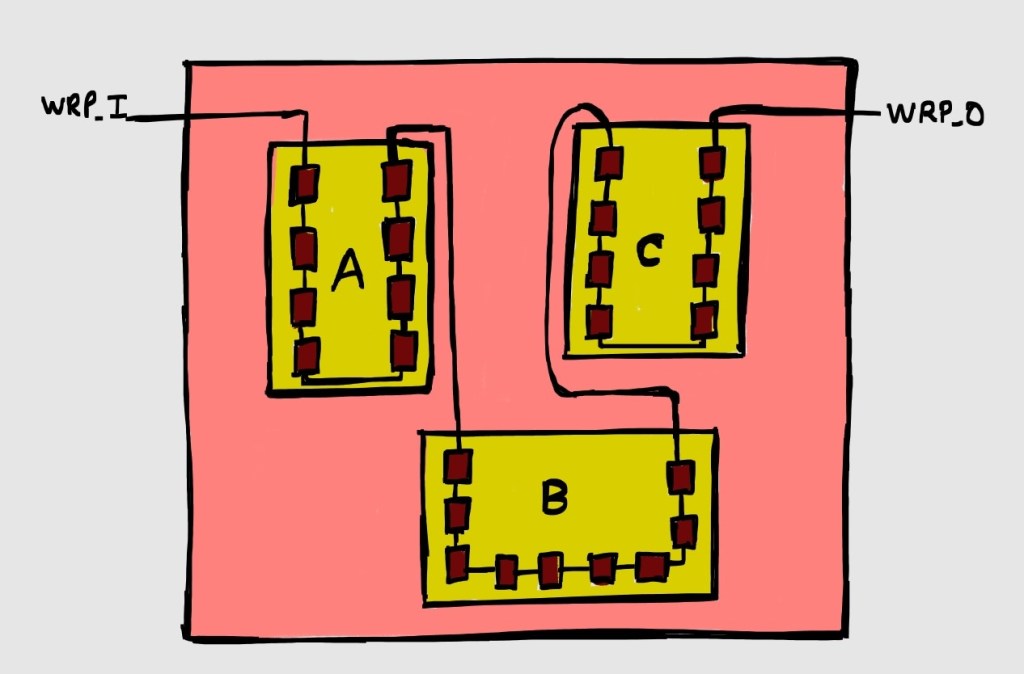

Wrapper chains are formed by the scan cells around the boundary of the design. Assuming an SoC with different IPs, we can partition the design and each IP (or core) has its own set of wrapper chains. It basically isolates the core logic from the surrounding logic through wrapper chains between I/O ports of the core and the core-logic.

How it helps testing?

- When many wrapped cores are integrated in an SoC, we can choose the blocks we want to test and exclude the rest.

- A wrapped core can be tested individually, and when integrated in SoC, the testing of multiple instantiations of same wrapped core can be bypassed, by just using the wrapper chains.

- While accessing partition level IOs (Inputs and Outputs), they might have less controllability and observability from the top-level. Wrapper chains include such IOs and help in more exhaustive testing for such partitions

Figure 1 shows how wrapper chains look like in a design with partition ‘A’, ‘B’ and ‘C’.

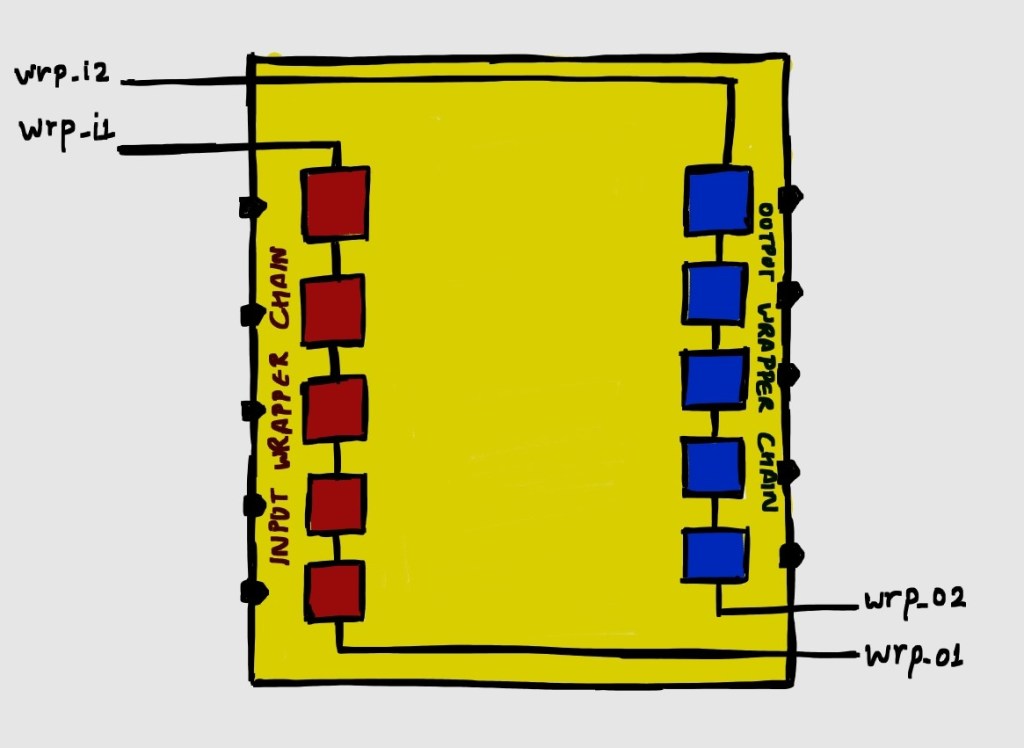

There are two kinds of wrapper chains:

- Input wrapper chains : connects sequential elements at input side of the submodule

- Output Wrapper Chains : connects sequential elements at output side of the submodule

The sequential elements in the wrapper chains are termed as wrapper cells. There are of two kinds:

- Shared (sharing the scan cell already present in the design)

- Dedicated (inserting a special wrapper cell to be used in input/output wrapper chain)

In a wrapper core (a module with defined wrapper chains), there can be two cases:

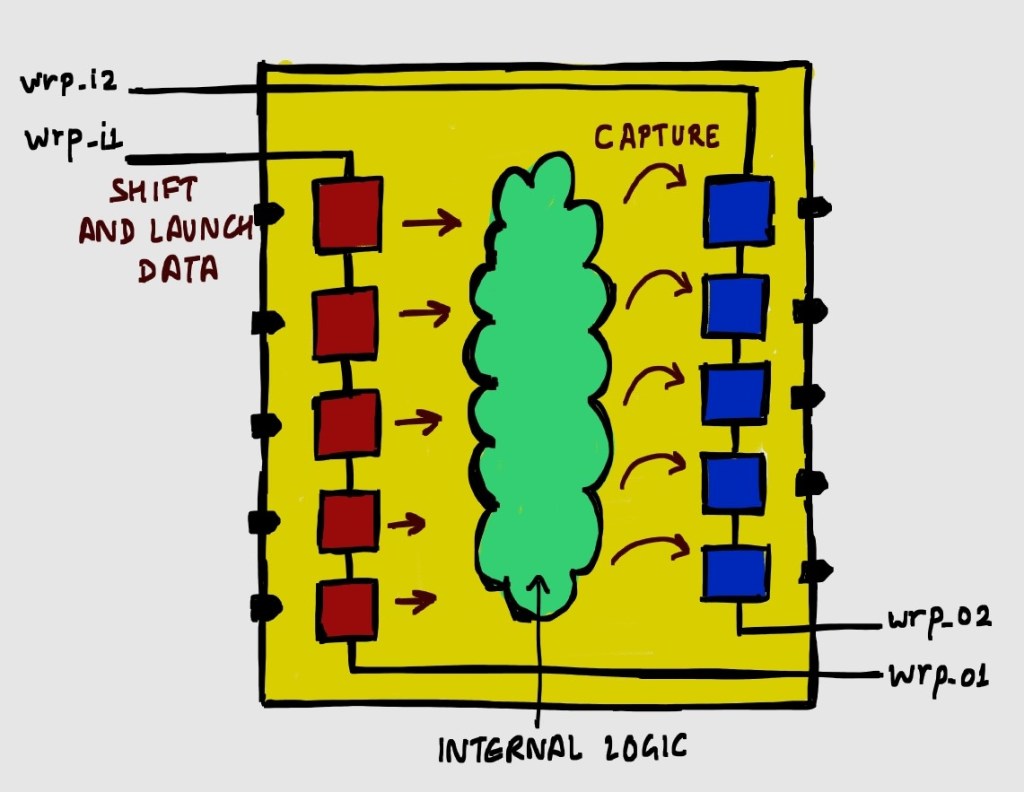

Testing the logic inside the partition/submodule (Internal/Intest mode)

- Input wrapper chains launch data into the inside logic and output wrapper chains capture data from inside logic.

- Outside data does not matter (core is isolated from outside logic).

- Input wrapper cells are in shift mode, output and core cells are allowed to capture.

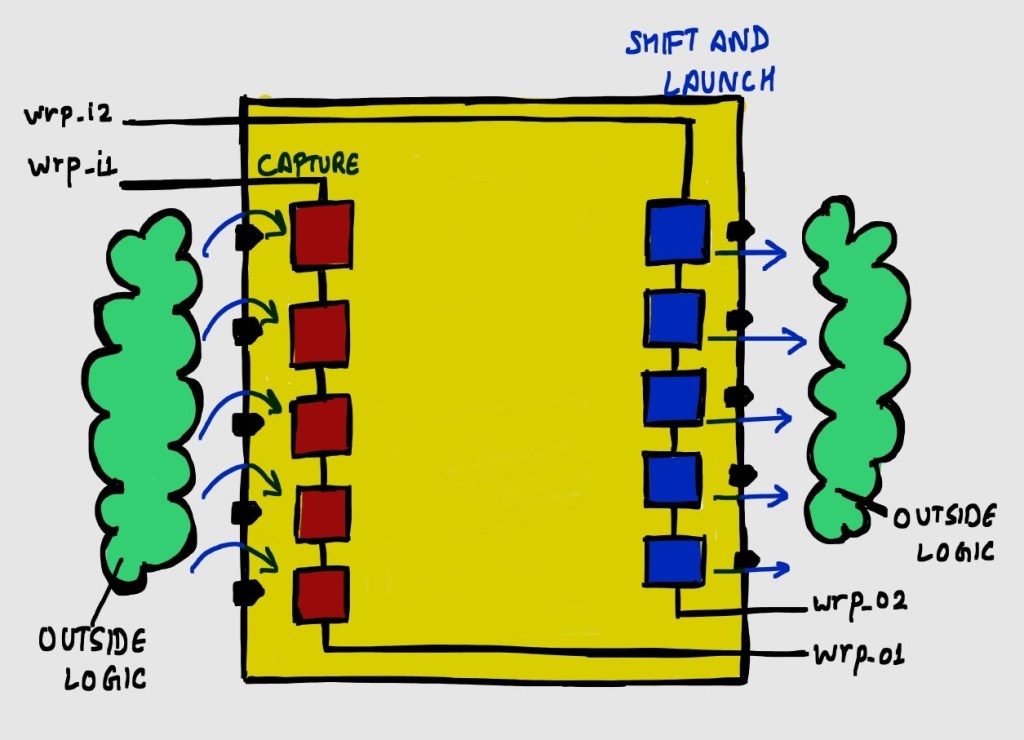

Testing the logic outside the partition/submodule (External/Extest mode)

- Output wrapper chains launch data into the outside logic and input wrapper chains capture data from outside logic.

- Inside logic does not matter.

- Output wrapper cells are in shift mode, core and input cells are allowed to capture

Input and Output wrapper chains have the same logic, only the enable is different. There are two different signals ‘intest_enable‘ and ‘extest_enable‘, to keep a control on which cells are launching and capturing data.

There are certain components which cannot be included in wrapper chains:

- Input ports which do not drive any sequential cell

- Clock ports/Bidirectional Ports

- DFT signals

- Floating outputs

Leave a comment